Здравствуйте, друзья.

Пришла в голову мысль опубликовать последние события за месяц (январь 2020) из мира FPGA/ПЛИС. Ниже списком приведены несколько ссылок на новости, анонсы, вебинары, воркшопы, туториалы, видео и тд. Если данный формат будет интересен, будем собирать новости по крупицам из интернета. Подобные новостные дайджесты есть, например, на хабе про php, почему бы и не сделать что-то подобное и для ПЛИС?

Новостной дайджест событий из мира FPGA/ПЛИС — №004 (2020_04)

Здравствуйте, друзья.

Пришла в голову мысль опубликовать последние события за месяц из мира FPGA/ПЛИС. Ниже приведены несколько ссылок на новости, анонсы, вебинары, воркшопы, туториалы, видео и тд. Подобные новостные дайджесты есть, например, на хабе про php, почему бы и не сделать что-то подобное и для ПЛИС?

Подробности в конце статьи ;)

Intel перезапустила компанию Altera по производству ПЛИС и обновила линейку программируемых чипов Agilex

В конце февраля 2024 года Intel перезапустила на рынок компанию Altera по производству ПЛИС (field-programmable gate array, FPGA) и представила обновлённую линейку программируемых чипов под названием Agilex, включая Agilex 9, Agilex 7 F-серии и I-серии, Agilex 5 и Agilex 3.

Экскурсия по Музею Истории Компьютеров в Калифорнии, с пользой для разработки. Часть 1. ENIAC, Stretch, CDC6600, IBM/360

Каким образом все это принесет пользу России? Под такие проекты мы собираемся раздавать FPGA платы на конференции которая пройдет 18-22 сентября в Томске. Туда приедут представители МГУ, МФТИ, МИЭТ, МЦСТ, Imagination Technologies, National Instruments итд. Они будет обсуждать, как обновить программу университетов, чтобы сегодняшние студенты через несколько лет проектировали росийские чипы на уровне передовых западных компаний. Там также будет школа-семинар, на которой будут обсуждать, как делать учебные процессоры — начиная от простейшего schoolMIPS от Станислава Жельнио sparf.

Вот первая фотография из музея в Маунтин-Вью — на ней помимо Ирины и ракеты в центре виден небольшой ящичек. Это бортовой компьютер космической станции «МИР» , который проектировали инженеры советского объединения «ЭЛАС», которое трансформировалось в современную зеленоградскую компанию «ЭЛВИС»:

Итак, темы для учебных проектов — начиная из дремучих десятилетий середины XX века:

От Торонто до Томска: подведение итогов и планирование будущих семинаров по микроэлектронике в России

Важная часть экспериментов с MIPSfpga случилась в России, на Украине и в Казахстане в течении двух прошлых лет — про это рассказала на конференции в Торонто Сара Харрис, профессор Университета Лас-Вегаса. В семинарах на эту и смежные темы проектирования чипов (Nanometer ASIC) приняли участие МГУ, МФТИ, МИФИ, МИЭТ, ИТМО и другие ведущие университеты.

Сейчас эксперимент продолжается: в этом месяце, помимо конференции в Томске, в Россию приезжает Роберт Оуэн, известный консультант по университетским образовательным программам в области микроэлектроники. За последние 23 года Роберт Оуэн посетил сотни университетов в Европе, Азии, Америке и даже Африке, как представитель Texas Instruments, ARM, Xilinx и Imagination. Он помогал университетам поставить программы в области DSP, микроконтроллеров, встроенных процессоров и систем на кристалле.

Вся эта деятельность — не абстрактное образование ради образования. На технологиях разработки микросхем с использованием языков описания аппаратуры Verilog и VHDL и использовании синтезируемых ядер стоит бизнес таких российских компаний как ЭЛВИС-НеоТек и Байкал Электроникс, о которых расскажет в лекции на этой неделе никто иной как Чубайс.

Про эти и другие мероприятия из прошлого и будущего подробнее под катом.

От песка к компьютеру. Часть 1. Атомы и транзисторы

Все мы еще с уроков информатики знаем, что информация внутри компьютера передаётся при помощи нулей и единиц, но оказалось, что большинство айтишников, с которыми я общаюсь (и довольно хороших!) слабо представляют, как же, все-таки, устроен компьютер.

Все мы еще с уроков информатики знаем, что информация внутри компьютера передаётся при помощи нулей и единиц, но оказалось, что большинство айтишников, с которыми я общаюсь (и довольно хороших!) слабо представляют, как же, все-таки, устроен компьютер. Как заставить песок делать то, чего мы от него хотим?

Для большинства людей познания устройства компьютера оканчиваются на уровне его составных элементов — процессор, видеокарта, оперативная память… Но что именно происходит внутри этих чёрных прямоугольничков после подачи питания — магия. В этой статье (скорей всего, даже серии статей) я постараюсь простым языком объяснить, как же устроены эти таинственные прямоугольнички.

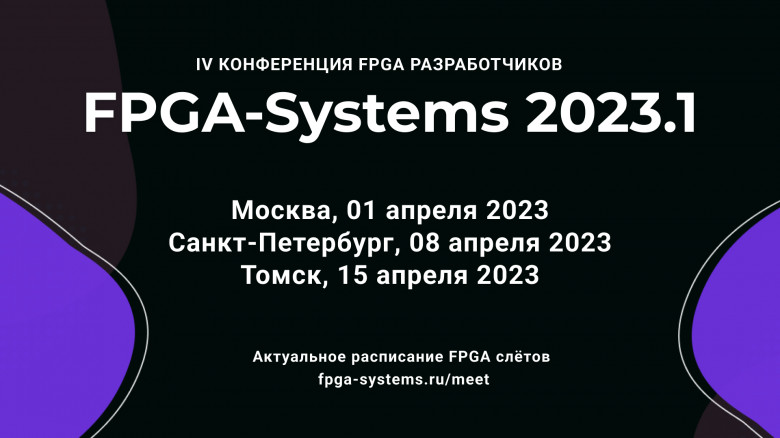

IV Конференция FPGA разработчиков: Мск, СПб и Томск

ПЛИС-культ привет, FPGA хаб!

В очередной раз мы собираемся нашим ламповым FPGA комьюнити для обмена опытом, всякими премудростями и просто для общения в кругу таких же ПЛИСоводов как и ты.

Программа уже сформирована, регистрация открыта и возможно тебе повезет стать частью фактически единственного FPGA движа на постсоветском пространстве. Не откладывай на завтра и регистрируйся на IV конференцию FPGA-Systems 2023.1.

Made at Intel. Acquisitions -3

Сегодня у нас на очереди третья заключительная часть повествования о приобретениях Интел (начало – здесь и здесь). Я сразу оговаривался о том, что вряд ли смогу осветить всю M&A активность, поэтому сфокусируюсь на наиболее знаковых и памятных событиях за 22 года моей работы в компании. Начнем, пожалуй, с Альтеры.

Сетевой JTAG программатор для Altera Quartus Prime из Raspberry Pi3

Выпущено программное обеспечение, которое позволяет сделать из Raspberry Pi3 сетевой JTAG программатор для САПР Altera Quartus Prime. Это решение позволяет удаленно загружать FPGA Altera/Intel и даже вести удаленную отладку с помощью инструмента SignalTap. Далее расскажу,

как использовать это ПО.

Суровая сибирская и казахстанская микроэлектроника 2017 года: Verilog, ASIC и FPGA в Томске, Новосибирске и Астане

Для перехода от единичных успехов к развитой экосистеме необходимо подкрутить образование. В сентябре в Томске прошло совещание, на котором преподаватели и инженеры из Москвы, Сибири, Поволжья, Калифорнии и других мест обменялись опытом в преподавании микроэлектроники. Одновременно там же прошел учебный семинар по SystemVerilog, VHDL, FPGA, CPU IP, на который пришли не только россияне, но и студенты из Китая и Вьетнама, среди которых быстро распостранилась информация, что рядом учат чему-то полезному для их карьеры. Под катом — отчет об этом и сопутствующих событиях. Действующие лица: томские и новосибирские университеты, московские МГУ, МФТИ и МИЭТ, новосибирские лицеи, российская компания МЦСТ, американские MIPS, AMD и National Instruments, британская Imagination и казахский Назарбаевский Университет.

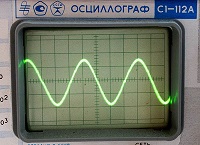

Функциональный DDS rенератор на ПЛИС

Недавно я увидел проект генератора сигналов на микроконтроллере AVR. Принцип генерации — DDS, на базе библиотеки Jesper максимальная частота — 65534 Гц (и до 8 МГц HS выход с меандром). И тут я подумал, что генератор — отличная задача, где ПЛИС сможет показать себя в лучшем виде. В качестве спортивного интереса я решил повторить проект на ПЛИС, при этом по срокам уложиться в два выходных дня, а параметры получить не строго определенные, а максимально возможные. Что из этого получилось, можно узнать под катом

Недавно я увидел проект генератора сигналов на микроконтроллере AVR. Принцип генерации — DDS, на базе библиотеки Jesper максимальная частота — 65534 Гц (и до 8 МГц HS выход с меандром). И тут я подумал, что генератор — отличная задача, где ПЛИС сможет показать себя в лучшем виде. В качестве спортивного интереса я решил повторить проект на ПЛИС, при этом по срокам уложиться в два выходных дня, а параметры получить не строго определенные, а максимально возможные. Что из этого получилось, можно узнать под катомОбновление Linux в устройстве на базе чипа Altera SoC FPGA и получение доступа к расшаренным ресурсам Windows-сервера

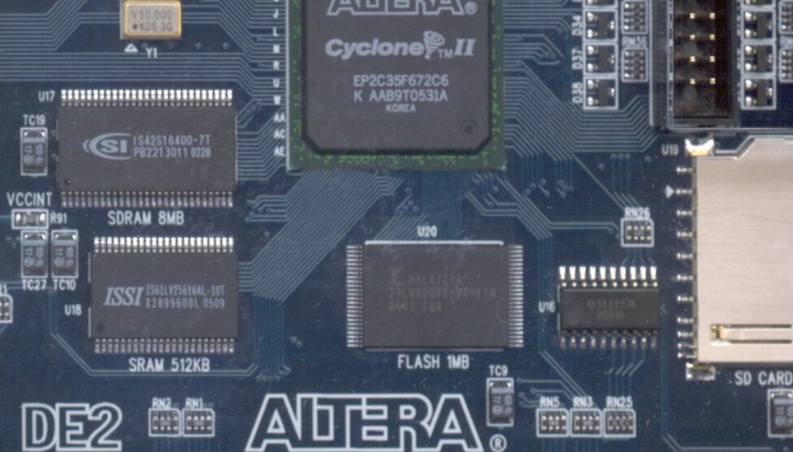

Недавно компания Terasic начала продажи весьма интересной платы DE0-Nano-SoC Kit. Интересна она тем, что за весьма скромную цену предлагается очень мощный и функционально-насыщенный комплект разработчика на основе чипа Altera Cyclone V SoC FPGA со встроенным двухъядерным процессором ARM Cortex-A9. Кроме того, производитель в комплекте с платой даёт ОС Linux, развёрнутую на карту памяти MicroSD.

Но получив эту плату в своё распоряжение, я довольно быстро наткнулся на несколько проблем, обусловленых тем, что Linux был скомпилирован из исходников Yocto Project. В основном все проблемы были связаны с отсутствием общедоступных репозиториев, из которых можно было бы добавить в систему недостающие компоненты. Например, для того, чтобы получить доступ с этого устройства через сеть к расшаренным ресурсам Windows-сервера, в ядре не хватало модуля поддержки файловой системы Cifs.

Поэтому прежде всего было решено обновить ядро, заменить Yocto на более привычный Debian Wheezy и доустановить всё, что необходимо для доступа к расшаренным ресурсам Windows-сервера.

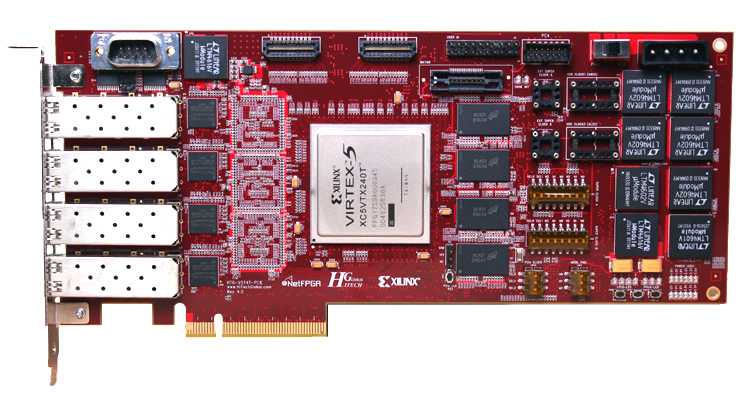

Ethernet + PCIe + FPGA = LOVE

Доступ по Ethernet невозможен без сетевых карточек (NIC). На небольших скоростях (до 1G) NIC встраивают в материнки, а на больших (10G/40G) NIC размещается на отдельной PCIe плате. Основным ядром такой платы является интегральный чип (ASIC), который занимается приемом/отправкой пакетов на самом низком уровне. Для большинства задач возможностей этого чипа хватит с лихвой.

Что делать, если возможностей сетевой карточки не хватает? Либо задача требует максимально близкого доступа к низкому уровню? Тогда на сцену выходят платы с перепрограммируемой логикой — ПЛИС (FPGA).

Какие задачи на них решают, что размещают, а так же самых интересных представителей вы увидите под катом!

Осторожно, будут картинки!

Altera + OpenCL: программируем под FPGA без знания VHDL/Verilog

Всем привет!

Altera SDK for OpenCL — это набор библиотек и приложений, который позволяет компилировать код, написанный на OpenCL, в прошивку для ПЛИС фирмы Altera. Это даёт возможность программисту использовать FPGA как ускоритель высокопроизводительных вычислений без знания HDL-языков, а писать на том, что он привык, когда это делает под GPU.

Я поигрался с этим инструментом на простом примере и хочу об этом вам рассказать.

План:

- Пару слов об FPGA

- На чём запускать?

- Процесс разработки (workflow)

- OpenCL BSP

- Компилируем кернел

- … и запускаем

- Заключение

Добро пожаловать под кат! Осторожно, будут картинки!

Altera + OpenCL: вскрываем ядро

Всем привет!

В прошлой статье я запустил простой OpenCL пример на FPGA фирмы Altera:

// ACL kernel for adding two input vectors

__kernel void vector_add( __global const uint *restrict x,

__global const uint *restrict y,

__global uint *restrict z )

{

// get index of the work item

int index = get_global_id(0);

// add the vector elements

z[index] = x[index] + y[index];

}

Я намеренно не углублялся в детали и показал верхушку айсберга: процесс разработки, сборку проекта, запуск на системе.

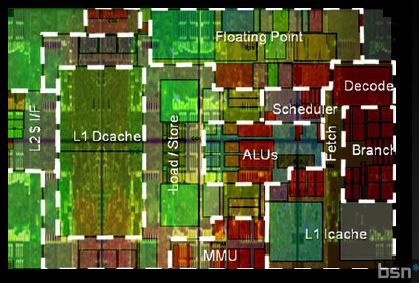

При подготовке первой статьи мне стало дико интересно, во что превращаются (со стороны FPGA) эти строчки. Понимание архитектуры даст возможность что-то соптимизировать и понять на что уходят ресурсы, а так же что хорошо и плохо для этой системы.

В этой статье мы попробуем вскрыть ядро и найти ответы на следующие вопросы:

- Какая у него архитектура?

- Как происходит его настройка? Как попадают данные на обработку?

- На какой частоте он работает? Чем это определяется?

- Можно ли просимулировать только ядро в RTL-симуляторах?

- Какие блоки занимают больше всего ресурсов? Можно ли как-то это соптимизировать?

Давайте взглянём на его внутренности! Добро пожаловать под кат!

Готовимся к Сколковской Школе Синтеза Цифровых Схем: литература, FPGA платы и сенсоры

Мы с коллегами из МИЭТ, Ядро Микропроцессоры / Syntacore, МИРЭА, ВШЭ МИЭМ, МГУ, Иннополиса, ЧНТУ, Самарского университета, Siemens EDA и с поддержкой от Cadence Design Systems - проводим, начиная с 30 октября, курс на 13 суббот под названием "Сколковская Школа Синтеза Цифровых Схем". Это сильно расширенная версия трехдневной школы на ChipEXPO, которая прошла на ура в сентябре.

Суть школы - знакомство с маршрутом проектирования RTL2GDSII, который применяют проектировщики чипов в Apple, Intel итд, используя в качестве тренажера лабы на микросхемах реконфигурируемой логики FPGA, как это делают например в MIT в курсе 6.111. Помимо лаб на FPGA в курсе будет туториал по ASIC flow используя софтвер от Cadence, после которого, если мы договоримся, будет экскурсия на фабрику микросхем в Зеленограде.

Число регистраций снова в несколько раз превысило число посадочных мест в Сколково, поэтому большая часть участников вероятно будет проходить школу удаленно, как и зарегистрировавшиеся вне Москвы, в том числе в Белоруссии, Украине, Азербайджане, Казахстане итд - среди зарегистрировашихся есть даже русские живущие в Германии.

Сравнение плат Arduino – Марсоход

С чего начать? Пожалуй есть две интересные возможности – это плата Arduino или плата Марсоход. Попробую объяснить, что же это такое.

Как разработать микросхему, от идеи до результата. Часть 1. Теория

Как разработать микросхему, от идеи до результата. Часть 2. Установка программного обеспечения

Напоминаю, что я продолжаю идти к цели — сделать свой собственный Отечественный Процессор (TM). Продолжение процесса разработки можно посмотреть под катом.

Как разработать микросхему, от идеи до результата. Часть 3. Схемотехническое представление и Layout

В этой части мы:

- Будем рисовать схему, используя XSCHEM

- Произведём симуляцию нашей схемы, используя NGSPICE

- Поймём цикл производства микросхемы

- Нарисуем Layout, используя KLayout

Предполагается, что вы уже прочитали предыдущие материалы. Если мне удалось вас заинтересовать, прошу под кат!