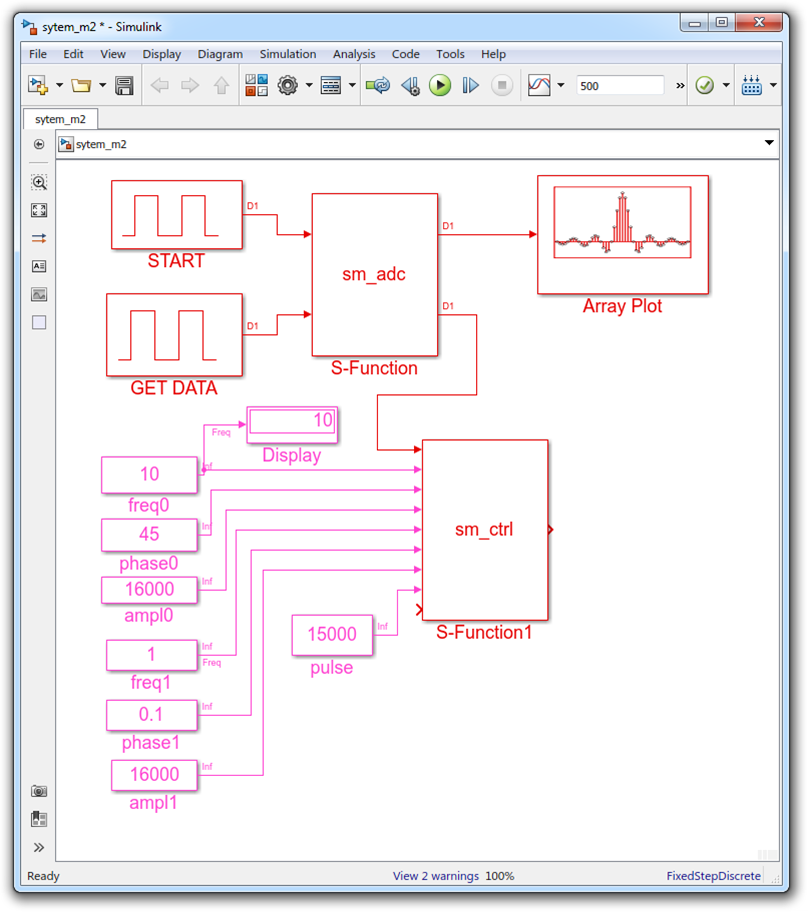

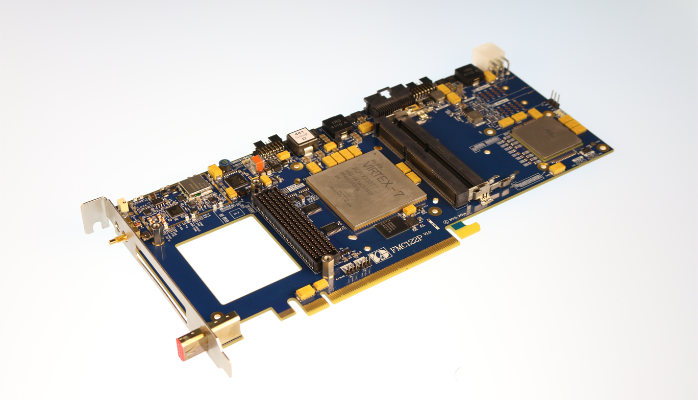

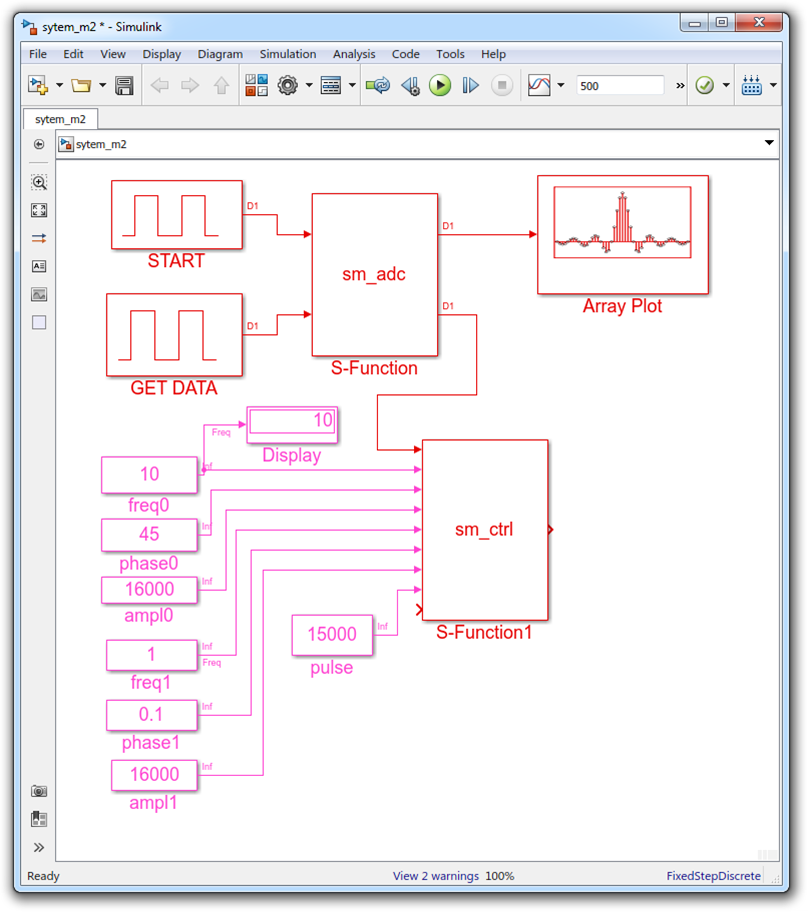

Важной практической задачей является использование Matlab/Simulink с реальной аппаратурой которая позволит принять сигнал из реального мира. Это очень полезно для отладки алгоритмов. В данной работе представлена технология подключения к Simulink устройств АЦП производства АО «ИнСис». Для подключения используется DLL, которая видна в Simulink как компонент sm_adc. Для работы с аппаратурой используется отдельная консольная программа. Связь с DLL производится через разделяемую память. По данной технологии могут быть подключены любые АЦП на любых несущих модулях АО «ИнСис». В работе представлена система из генератора A7_DAC и модуля сбора FMC128E/FM412x500M.

Данная работа демонстрировалась на конференции «Технологии разработки и отладки сложных технических систем» 27-28 марта 2018 года.

Данная работа демонстрировалась на конференции «Технологии разработки и отладки сложных технических систем» 27-28 марта 2018 года.